#### **Combinational Circuits**

Chapter 3

S. Dandamudi

#### Outline

- Introduction

- Multiplexers and demultiplexers

- \* Implementing logical functions

- \* Efficient implementation

- Decoders and encoders

- \* Decoder-OR implementations

- Comparators

- Adders

- \* Half-adders

- \* Full-adders

- Programmable logic devices

- \* Programmable logic arrays (PLAs)

- \* Programmable array logic (PALs)

- Arithmetic and logic units (ALUs)

#### Introduction

- Combinational circuits

- » Output depends only on the current inputs

- Combinational circuits provide a higher level of abstraction

- \* Helps in reducing design complexity

- \* Reduces chip count

- \* Example: 8-input NAND gate

- » Requires 1 chip if we use 7430

- » Several 7400 chips (How many?)

- We look at some useful combinational circuits

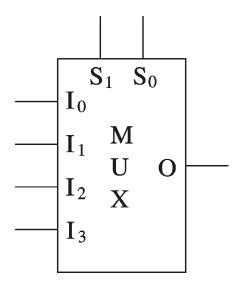

## Multiplexers

- Multiplexer

- \* 2<sup>n</sup> data inputs

- \* n selection inputs

- \* a single output

- Selection input determines the input that should be connected to the output

4-data input MUX

| $S_1$ | $S_0$ | О     |

|-------|-------|-------|

| 0     | 0     | $I_0$ |

| 0     | 1     | $I_1$ |

| 1     | 0     | $I_2$ |

| 1     | 1     | $I_3$ |

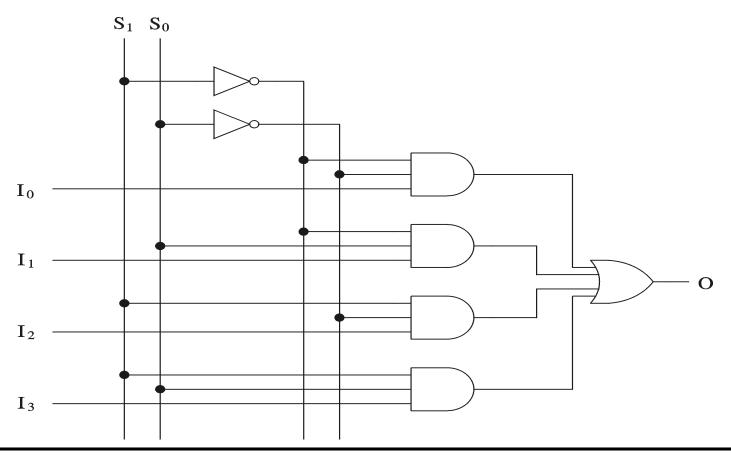

#### 4-data input MUX implementation

2003 © S. Dandamudi Chapter 3: Page 5

#### MUX implementations

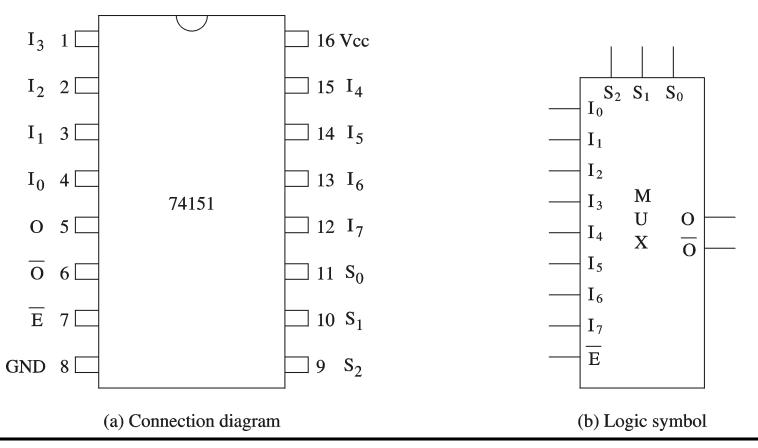

#### Example chip: 8-to-1 MUX

2003 © S. Dandamudi Chapter 3: Page 7

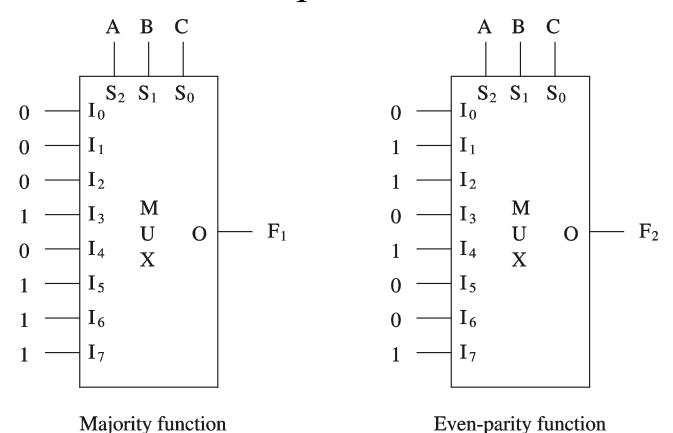

## Efficient implementation: Majority function

Original truth table

| A | В | C | F <sub>1</sub> |

|---|---|---|----------------|

| 0 | 0 | 0 | 0              |

| 0 | 0 | 1 | 0              |

| 0 | 1 | 0 | 0              |

| 0 | 1 | 1 | 1              |

| 1 | 0 | 0 | 0              |

| 1 | 0 | 1 | 1              |

| 1 | 1 | 0 | 1              |

| 1 | 1 | 1 | 1              |

New truth table

| A | В | $F_1$ |                                                                                              |

|---|---|-------|----------------------------------------------------------------------------------------------|

| 0 | 0 | 0     |                                                                                              |

|   |   |       | A                                                                                            |

| 0 | 1 | C     |                                                                                              |

|   |   |       | $0 \longrightarrow I_0^{S_1}$                                                                |

| 1 | 0 | C     |                                                                                              |

|   |   |       | $ \begin{array}{c} C \longrightarrow I_1 & M \\ C \longrightarrow I_2 & M \\ X \end{array} $ |

| 1 | 1 | 1     | $1 \longrightarrow \begin{bmatrix} \mathbf{I}_2 & \mathbf{X} \\ \mathbf{I}_3 \end{bmatrix}$  |

|   |   |       | 1 13                                                                                         |

|   |   |       |                                                                                              |

В

$S_0$

$\mathbf{F}_1$

M

U

X

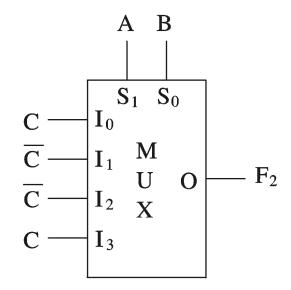

#### Efficient implementation: Even-parity function

Original truth table

| A | В | C | $F_1$ |

|---|---|---|-------|

| 0 | 0 | 0 | 0     |

| 0 | 0 | 1 | 1     |

| 0 | 1 | 0 | 1     |

| 0 | 1 | 1 | 0     |

| 1 | 0 | 0 | 1     |

| 1 | 0 | 1 | 0     |

| 1 | 1 | 0 | 0     |

| 1 | 1 | 1 | 1     |

New truth table

| A | В | $F_1$                   |

|---|---|-------------------------|

| 0 | 0 | C                       |

| 0 | 1 | $\overline{\mathbf{C}}$ |

| 1 | 0 | $\overline{\mathbf{C}}$ |

| 1 | 1 | С                       |

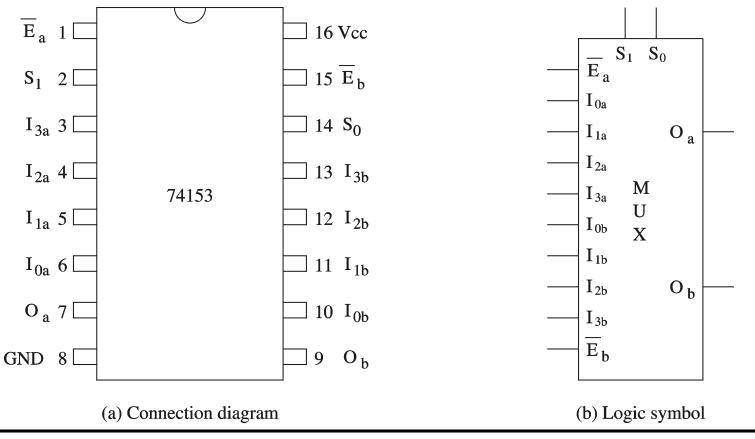

#### 74153 can used to implement two output functions

2003 © S. Dandamudi Chapter 3: Page 10

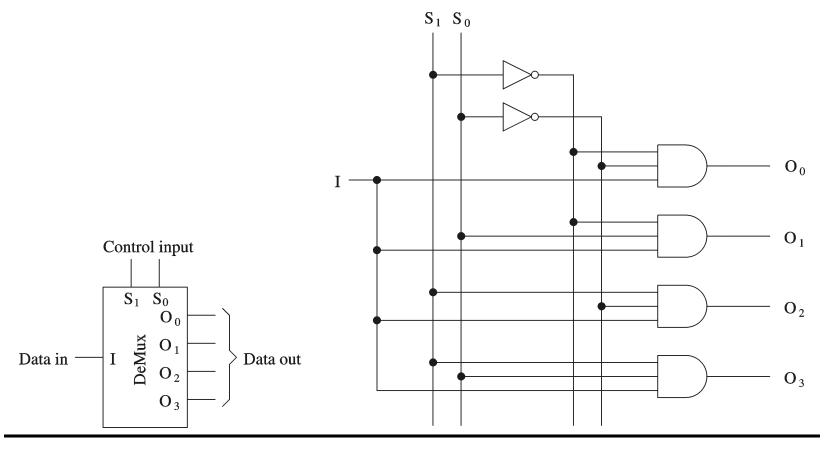

# Demultiplexers

# Demultiplexer (DeMUX)

2003 © S. Dandamudi Chapter 3: Page 11

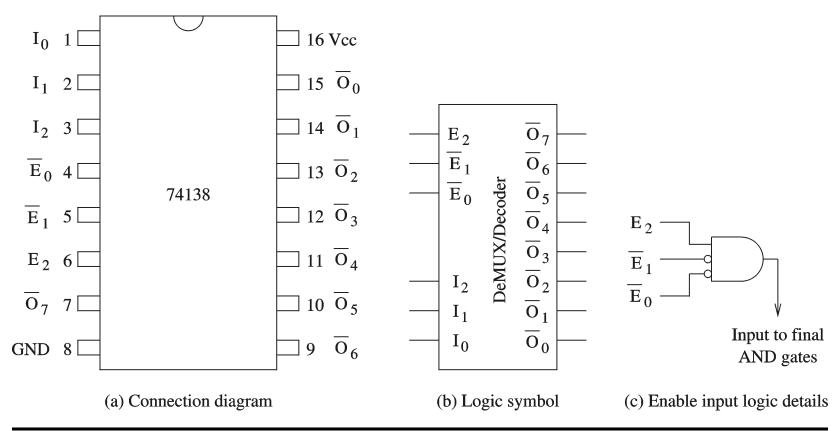

#### 74138 can used as DeMUX and decoder

© S. Dandamudi Chapter 3: Page 12

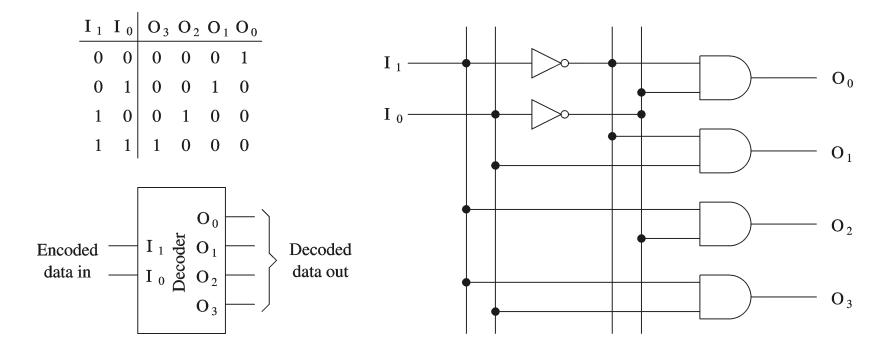

#### **Decoders**

#### Decoder selects one-out-of-N inputs

#### Decoders (cont'd)

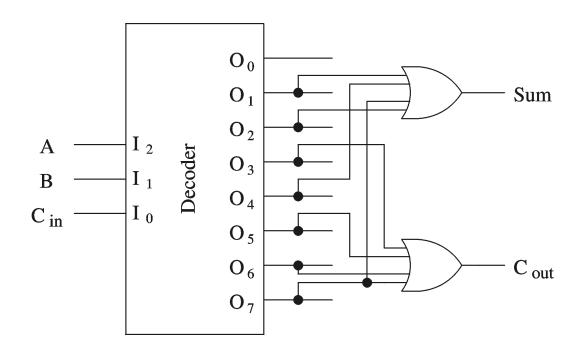

# Logic function implementation

| A | В | C <sub>in</sub> | Sum | C out |

|---|---|-----------------|-----|-------|

| 0 | 0 | 0               | 0   | 0     |

| 0 | 0 | 1               | 1   | 0     |

| 0 | 1 | 0               | 1   | 0     |

| 0 | 1 | 1               | 0   | 1     |

| 1 | 0 | 0               | 1   | 0     |

| 1 | 0 | 1               | 0   | 1     |

| 1 | 1 | 0               | 0   | 1     |

| 1 | 1 | 1               | 1   | 1     |

## Decoders (cont'd)

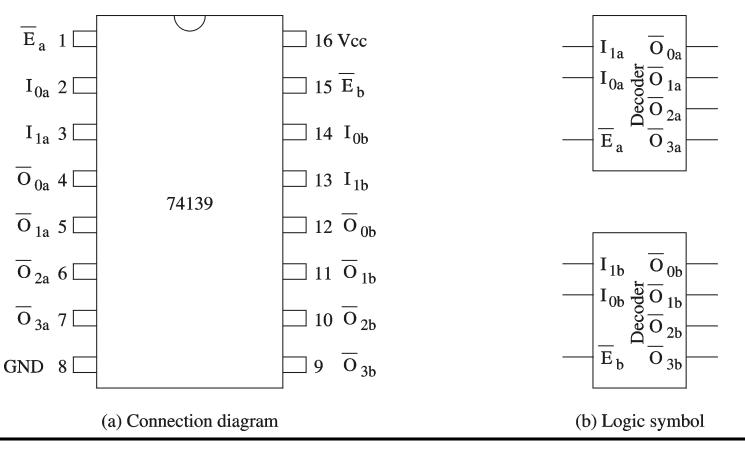

#### 74139: Dual decoder chip

2003 © S. Dandamudi

Chapter 3: Page 15

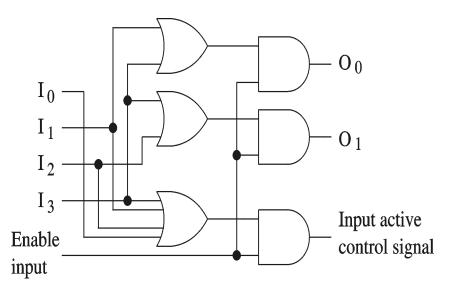

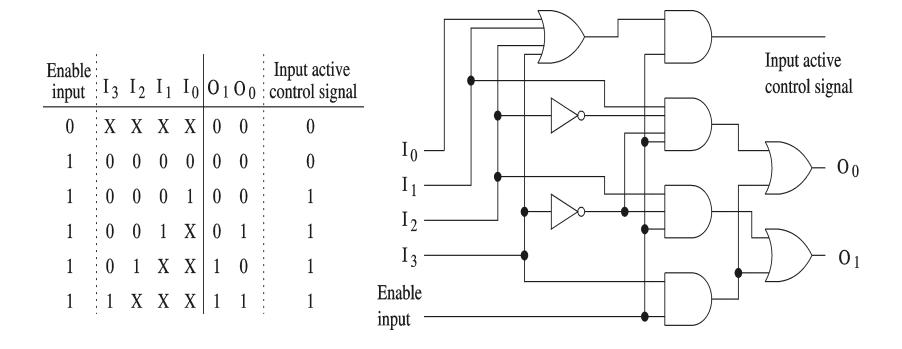

#### Encoders

#### Encoders

- \* Take  $2^B$  input lines and generate a B-bit binary number on B output lines

- \* Cannot handle more than one input with 1

| Enable input | I <sub>3</sub> | Ι2 | I <sub>1</sub> | $I_0$ | 01 | Ο 0 | Input active control signal |

|--------------|----------------|----|----------------|-------|----|-----|-----------------------------|

| 0            | X              | X  | X              | X     | 0  | 0   | 0                           |

| 1            | 0              | 0  | 0              | 0     | 0  | 0   | 0                           |

| 1            | 0              | 0  | 0              | 1     | 0  | 0   | 1                           |

| 1            | 0              | 0  | 1              | 0     | 0  | 1   | 1                           |

| 1            | 0              | 1  | 0              | 0     | 1  | 0   | 1                           |

| 1            | 1              | 0  | 0              | 0     | 1  | 1   | 1                           |

#### Encoders (cont'd)

#### Priority encoders

\* Handles inputs with more than one 1

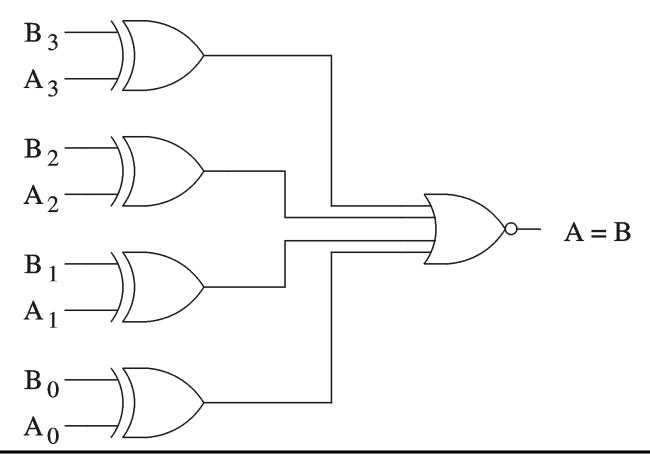

### Comparator

• Used to implement comparison operators  $(=, >, <, \ge, \le)$

© S. Dandamudi

Chapter 3: Page 18

## Comparator (cont'd)

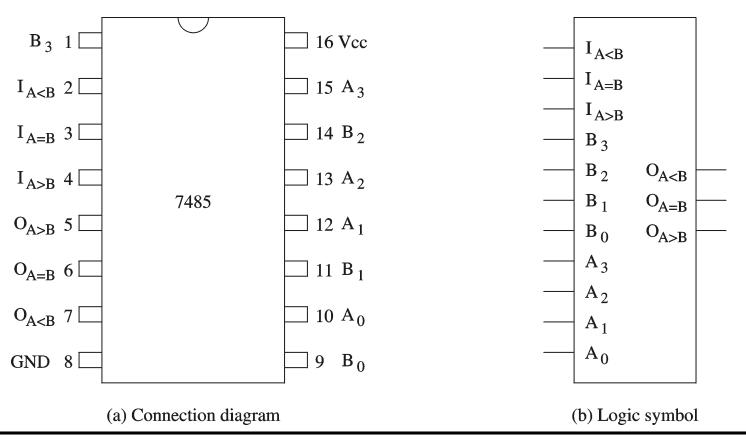

## 4-bit magnitude comparator chip

2003 © S. Dandamudi

Chapter 3: Page 19

#### Comparator (cont'd)

#### Serial construction of an 8-bit comparator

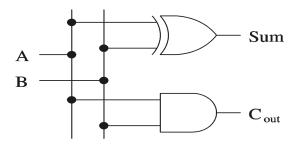

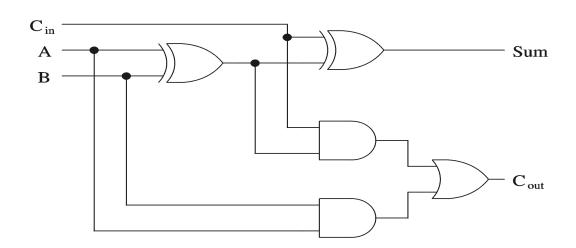

#### Adders

- Half-adder

- \* Adds two bits

- » Produces a *sum* and *carry*

- \* Problem: Cannot use it to build larger inputs

- Full-adder

- \* Adds three 1-bit values

- » Like half-adder, produces a *sum* and *carry*

- \* Allows building N-bit adders

- » Simple technique

- Connect Cout of one adder to Cin of the next

- » These are called *ripple-carry adders*

| Α | В | Sum | Cout |

|---|---|-----|------|

| 0 | 0 | 0   | 0    |

| 0 | 1 | 1   | 0    |

| 1 | 0 | 1   | 0    |

| 1 | 1 | 0   | 1    |

#### (a) Half-adder truth table and implementation

| A | В | $C_{in}$ | Sum | Cout |

|---|---|----------|-----|------|

| 0 | 0 | 0        | 0   | 0    |

| 0 | 0 | 1        | 1   | 0    |

| 0 | 1 | 0        | 1   | 0    |

| 0 | 1 | 1        | 0   | 1    |

| 1 | 0 | 0        | 1   | 0    |

| 1 | 0 | 1        | 0   | 1    |

| 1 | 1 | 0        | 0   | 1    |

| 1 | 1 | 1        | 1   | 1    |

(b) Full-adder truth table and implementation

2003

© S. Dandamudi

Chapter 3: Page 22

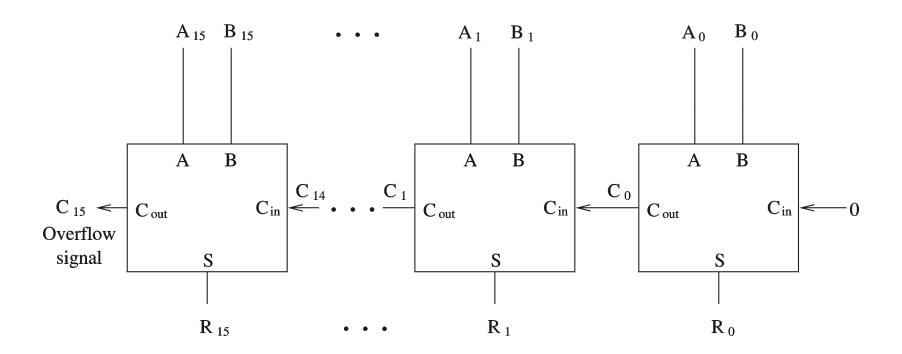

# A 16-bit ripple-carry adder

- Ripple-carry adders can be slow

- \* Delay proportional to number of bits

- Carry lookahead adders

- \* Eliminate the delay of ripple-carry adders

- \* Carry-ins are generated independently

```

» C_0 = A_0 B_0

» C_1 = A_0 B_0 A_1 + A_0 B_0 B_1 + A_1 B_1

» . . .

```

- \* Requires complex circuits

- \* Usually, a combination carry lookahead and ripple-carry techniques are used

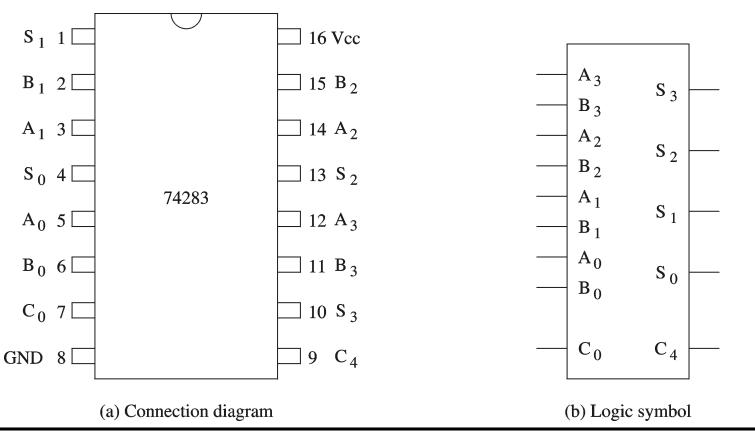

#### 4-bit carry lookahead adder

2003 © S. Dandamudi

Chapter 3: Page 25

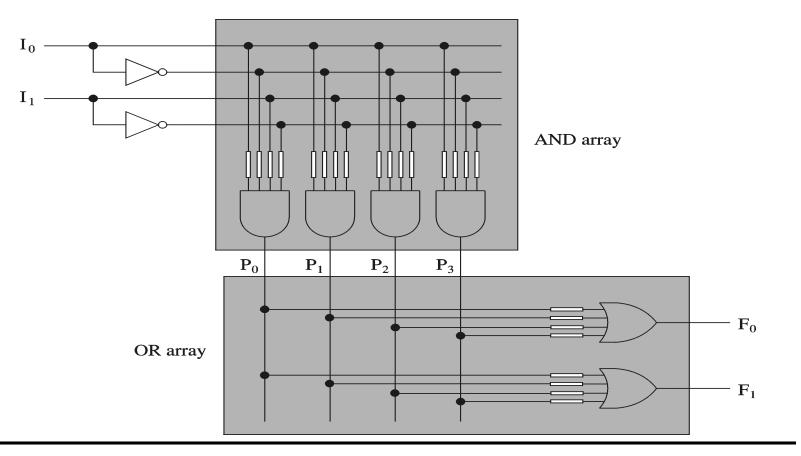

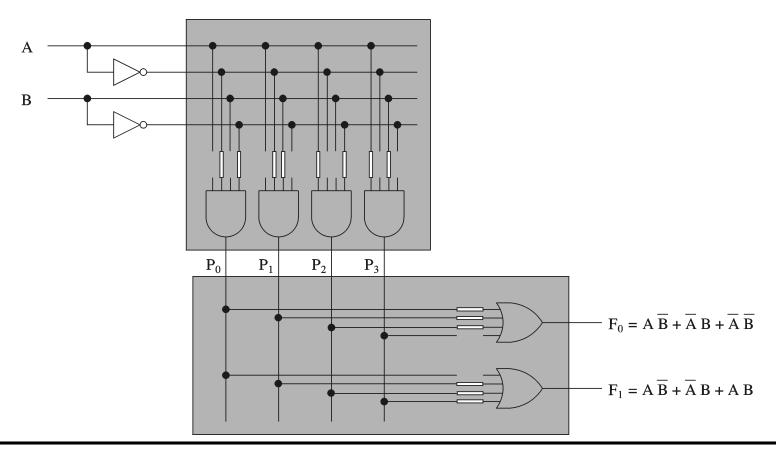

## Programmable Logic Arrays

#### PLAs

- \* Implement sum-of-product expressions

- » No need to simplify the logical expressions

- \* Take N inputs and produce M outputs

- » Each input represents a logical variable

- » Each output represents a logical function output

- \* Internally uses

- » An AND array

- Each AND gate receives 2N inputs

- $\rightarrow N$  inputs and their complements

- » An OR array

# Programmable Logic Arrays (cont'd)

#### A blank PLA with 2 inputs and 2 outputs

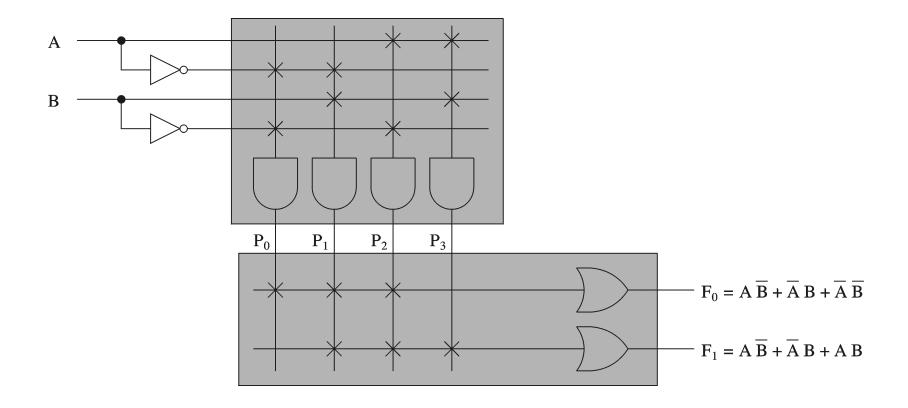

# Programmable Logic Arrays (cont'd)

#### Implementation examples

# Programmable Logic Arrays (cont'd)

#### Simplified notation

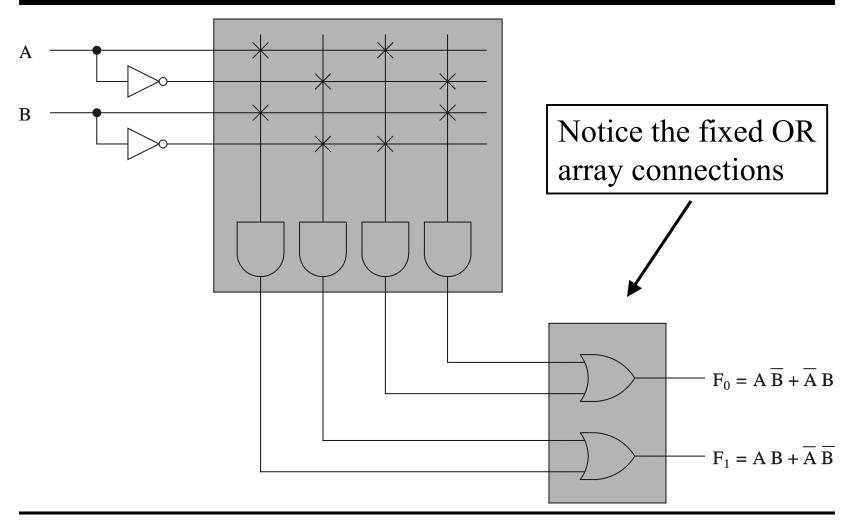

## Programmable Array Logic Devices

- Problem with PLAs

- \* Flexible but expensive

- \* Example

- » 12 X 12 PLA with

- 50-gate AND array

- 12-gate OR array

- » Requires 1800 fuses

- $-24 \times 50 = 1200$  fuses for the AND array

- $-50 \times 12 = 600$  fuses for the OR array

- PALs reduce this complexity by using fixed OR connections

- \* Reduces flexibility compared PLAs

### Programmable Array Logic Devices (cont'd)

2003 © S. Dandamudi Chapter 3: Page 31

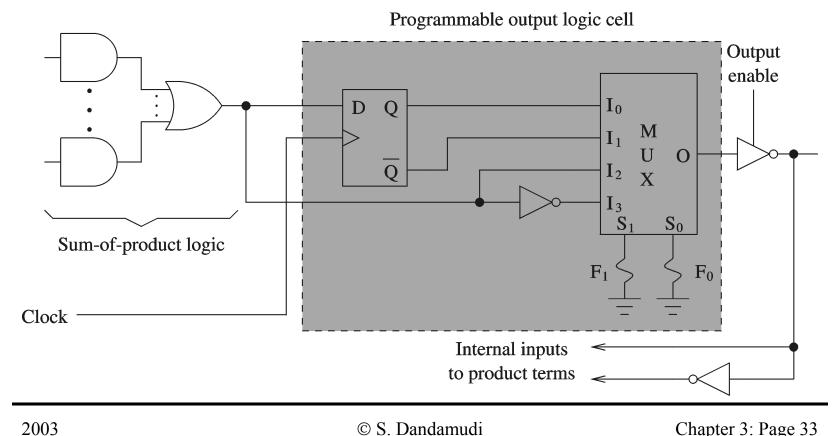

#### Programmable Array Logic Devices (cont'd)

- An example PAL (Texas Instruments TIBPAL22V10-10C)

- \* 22 X 10 PAL (24-pin DIP package)

- » 120-gate AND array

- » 10-gate OR array

- $* 44 \times 120 = 5280$  fuses

- » Just for the AND array

- OR array does not use any fuses

- \* Uses variable number of connections for the OR gates

- » Two each of 8-, 10-, 12-, 14-, and 16-input OR gates

- \* Uses internal feedback through a programmable output cell

## Programmable Array Logic Devices (cont'd)

- MUX selects the input

- S<sub>0</sub> and S<sub>1</sub> are programmed through fuses F<sub>0</sub> and F<sub>1</sub>

## Arithmetic and Logic Unit

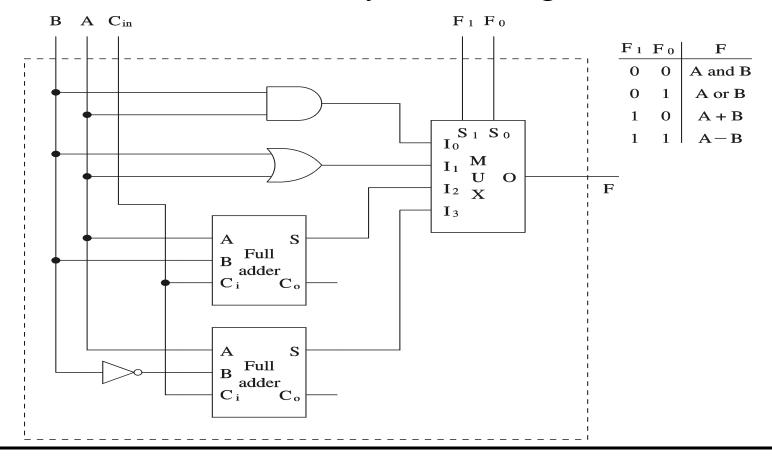

#### Preliminary ALU design

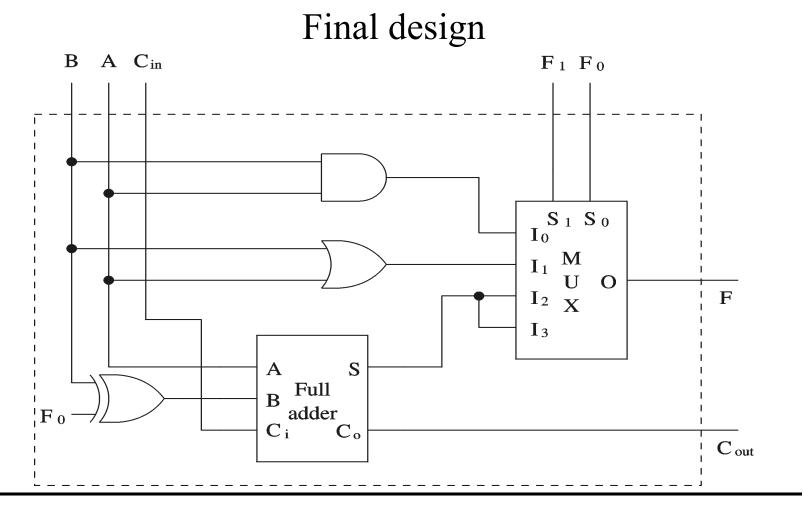

# Arithmetic and Logic Unit (cont'd)

2003 © S. Dandamudi Chapter 3: Page 35

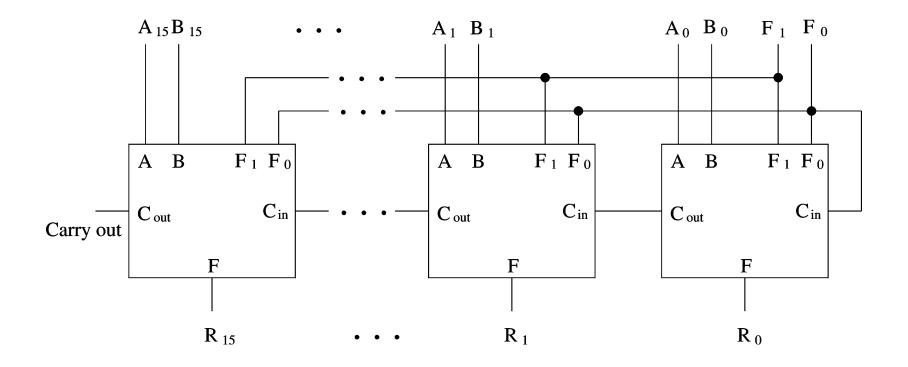

# Arithmetic and Logic Unit (cont'd)

#### 16-bit ALU

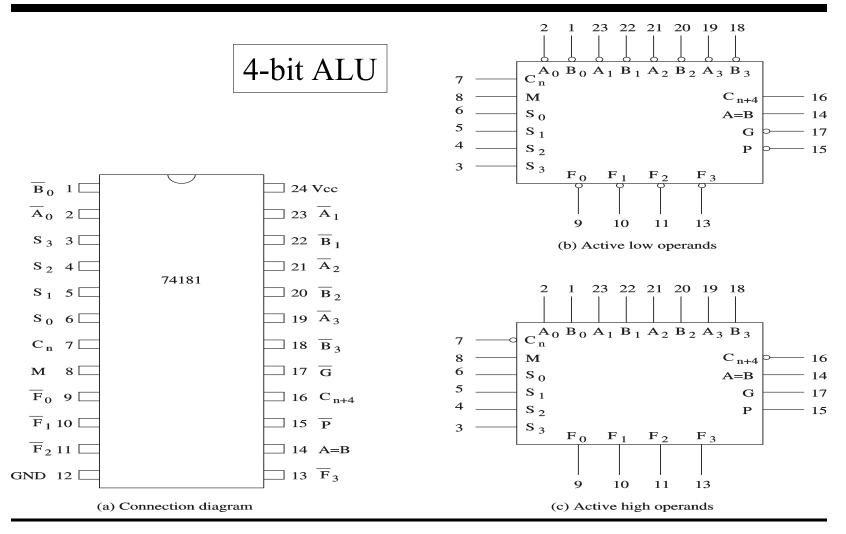

## Arithmetic and Logic Unit (cont'd)

2003 © S. Dandamudi

Chapter 3: Page 37

#### Summary

- Combinational circuits provide a higher level of abstraction

- \* Output depends only on the current inputs

- Sample combinational circuits

- \* Multiplexers and demultiplexers

- \* Decoders and encoders

- \* Comparators

- \* Adders

- » Half-adder

- » Full-adder

## Summary (cont'd)

- Programmable logic devices

- \* PLAs

- \* PALs

- Some more complete sets

- \* Multiplexers

- \* Decoder-OR

- \* PLAs

- \* PALs

- Looked at a very simple ALU design

Last slide